UG945 Vivado Design Suite Tutorial Using Constraints

文档 https://china.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/ug945-vivado-using-constraints-tutorial.pdf

https://www.xilinx.com/video/hardware/design-constraints-overview.html

概述:

XDC文件就是约束文件(限制文件),它是行业标准Synopsys®设计约束和专有的Xilinx®约束的组合

XDC的内容并不只是简单的字符串,而是Tcl命令的集合,会被顺序地读取和解析。。

所有的约束可以写在多个文件中,放在一个 约束集(Constraint set) 也可以直接在tcl console输入Constraint命令,可以用于调试。

综合好实现步骤都是时序驱动的,所以需要准确的时间限制定义。

Vivado工具是时序驱动的,限制不要过度定义也不要定义不足。过度定义可能会导致编译很长时间

对设计的约束不足会导致Vivado工具执行不必要的优化,例如检查具有多周期延迟的路径或错误的路径,并阻止将注意力集中在实际的关键路径上。

Lab1:定义时间约束异常

对应工程文件:project_cpu_netlist

set as target Constraint File.目标XDC文件中存储项目的所有的约束内容。

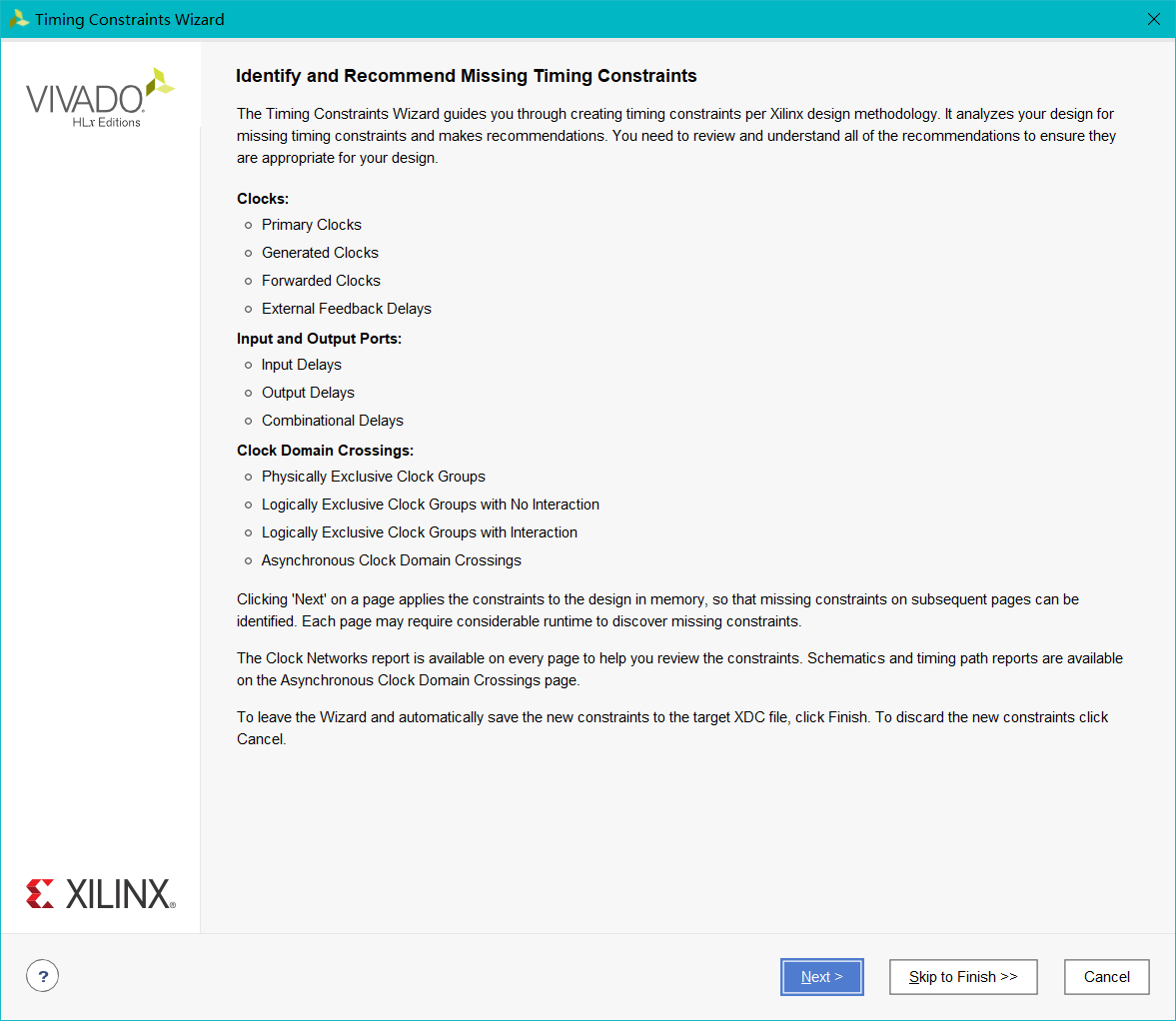

使用Timing Constraint Wizard

Open Synthesized Design下面有Timing Constraint Wizard

Timing Constraint Wizard可以用来生成约束我猜这个应该是生成一些时间约束的

timing Constraint wizard可以生成的约束介绍:需要阅读一下

分析缺少的时间约束,然后推荐一些时间约束。所以需要自己再看一遍,确保是正确的。

Timing Constraint Wizard向导的Primary Clock页面显示缺少时钟定义的所有时钟源

对于示例工程,向导检测了对逻辑路径进行计时所需的五个丢失的时钟约束,以及仅用于验证脉冲宽度和最小或最大周期要求的四个丢失的时钟约束。

在Recommend Constraint框里面,频率或者周期填一个另一个就自动会算出来,不想对某一行的信号添加约束就直接把最前面的核取方块取消即可。

forwarded clock是在FPGA的主输出端口上生成的时钟

External Feedback delay:FPGA外部的MMCM或PLL反馈延迟用于在时序报告中计算时钟延迟补偿 看不懂什么意思

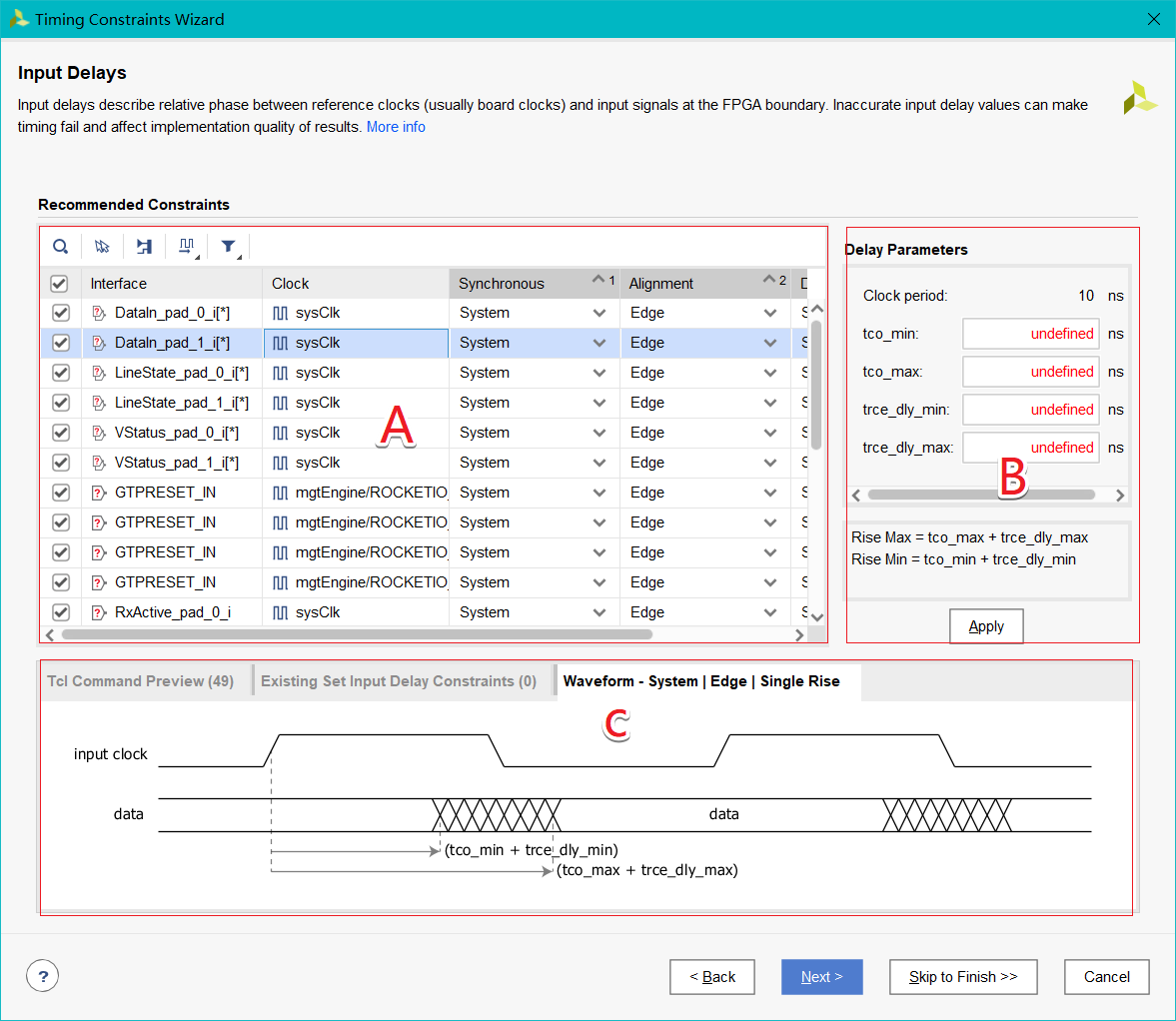

input delay

output delay

显示的是工程中所有未定义约束的输出信号

Combinational Delays

这个页面关注的是工程中未定义约束的组合路径,组合路径是遍历FPGA而不被任何顺序元素(sequential element)捕获的路径

Physically exclusive clock groups(互斥时钟组)

就是在工程中不同时存在的时钟

Logically exclusive clocks with no interaction(无交互的逻辑上互斥时钟组)

是同时处于活动状态的时钟,但共享时钟树部分除外。他们之家没有逻辑路径并且在共享部分之外,他们是互斥的

Logically exclusive clocks with interaction(有交互的逻辑上互斥时钟组)

是同时处于活动状态的时钟,但共享时钟树部分除外。当这些时钟之间具有逻辑路径时,仅限于共享时钟树部分的时钟在逻辑上是互斥的

Asynchronous Clock Domain Crossings (异步时钟域交叉)

异步时钟域交叉页面会给出一些安全时钟域交叉约束的建议

Timing Constraint Wizard这里面究竟在说些什么??完全没看懂

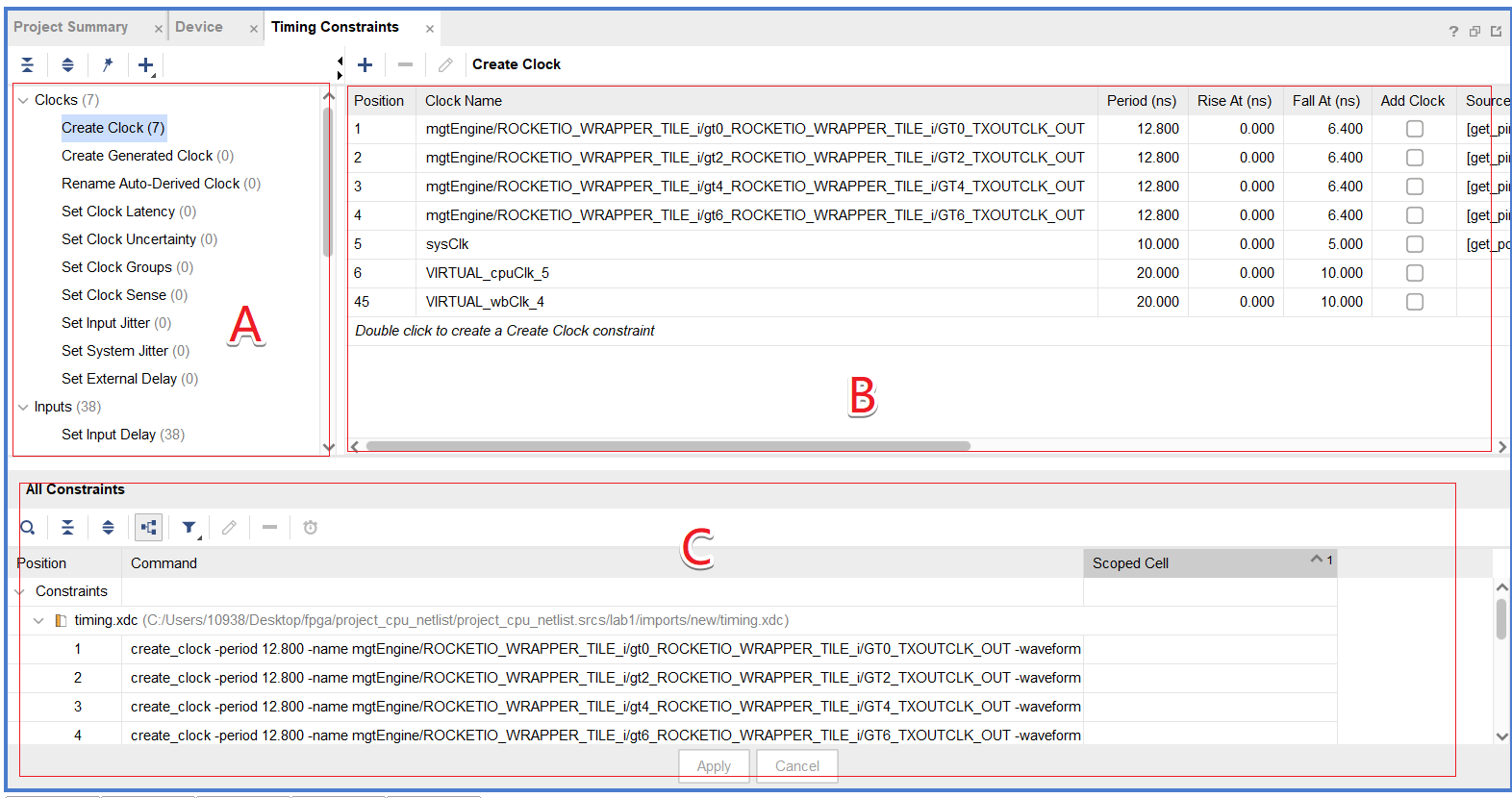

使用约束编辑器

Open Synthesis Design->Edit Timing Constraint

本文章使用limfx的vsocde插件快速发布