数据传输模块与信号交流模块结合

模块结合思路

总体思路:主卡向子卡发送控制信号,子卡获取控制信号后,根据信号内容改变当前状态。初态为stop,接收01信号后跳转到working状态;working状态接受00信号后跳转回stop状态。stop状态下,子卡采样时钟信号始终为低电平;working状态下,子卡采样时钟信号与外部输入信号一致。

经过测试发现,如果stop状态下接收到01信号后直接跳转到working状态,而此时外部的采样时钟信号在此之前已经为高电平,则可能导致本轮采样的采样时钟信号高电平时间不足,子卡无法完成采样,状态跳转出现异常。

解决思路:设置stop与working状态之间的中间状态waiting1,stop状态下接收01信号后,跳到waiting状态,此时先不同步外部的采样时钟信号,等待采样时钟信号出现上升沿后再跳转working状态同步。

working状态接收00信号后同样需要设置中间状态,保证本轮采样循环能够正常进行并结束,encode模块状态机能够正常跳转到data_waiting。思路也一致,中间状态waiting2下,采样时钟信号依然与外部信号同步,之后等待外部采样时钟信号下降沿后才跳回stop状态。

上板测试结果

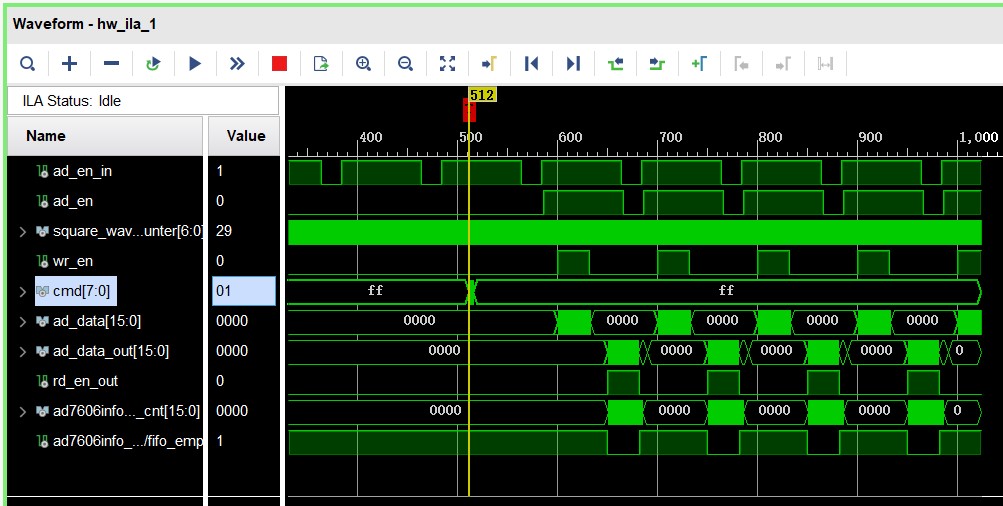

初态下,通过串口发送01信号,ila抓取结果:

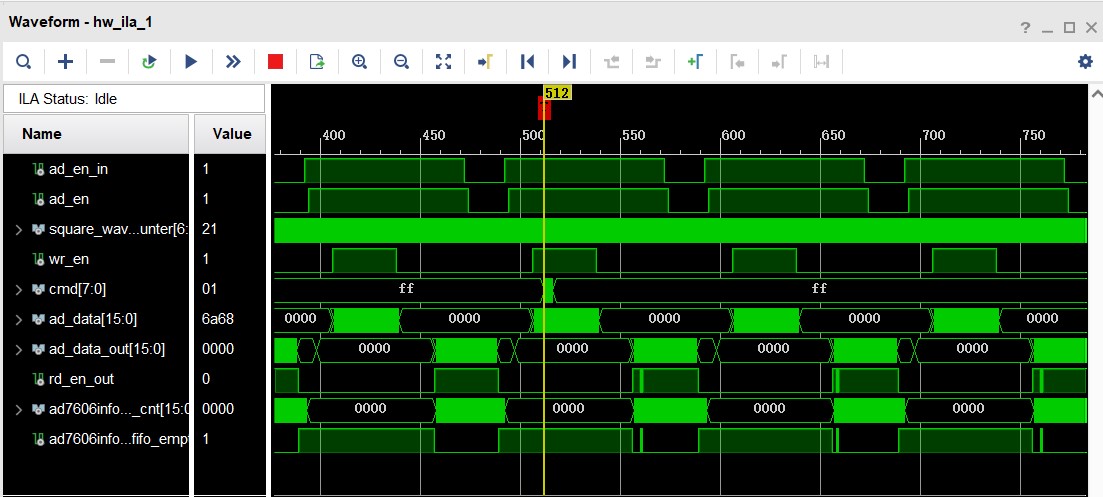

抓取后等待一段时间,在working状态下发送01,观察系统是否工作正常:

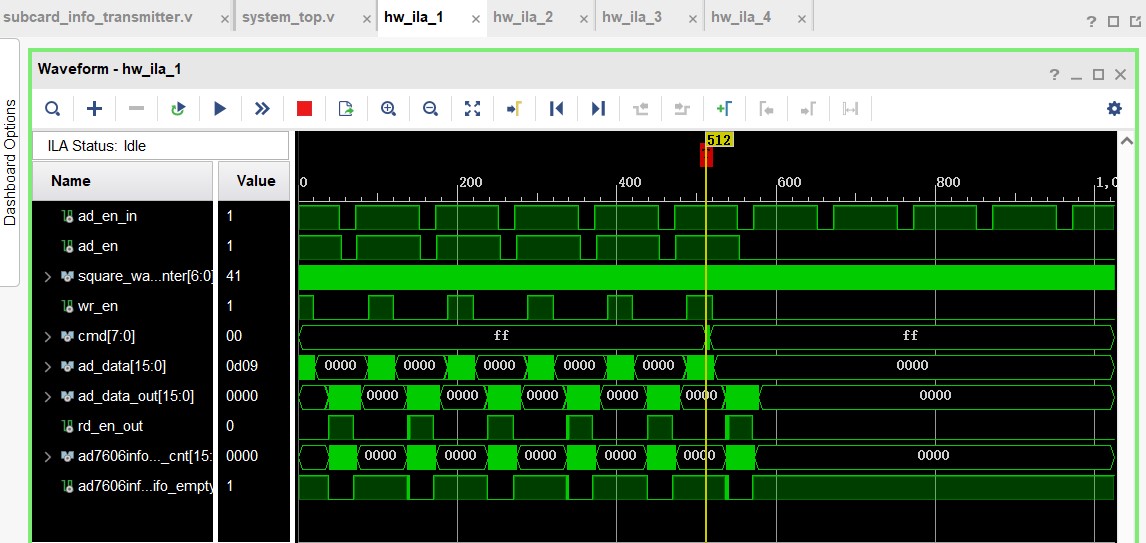

之后发送00,系统停止采集信号,观察ila抓取结果:

后续计划

目前还需要完善的工作以及后面的计划安排:

- 优化串口指令对编码模块的控制;

- 尝试将一块板子同时接收发送数据的功能拆分成两块板子,一块接收一块发送。

本文章使用limfx的vscode插件快速发布