编码解码模块设计

编码模块设计

数据常量定义:

parameter AD_IN_DW = 16 , //每个ad数据位宽

parameter AD_IN_CHANNEL = 32 , //ad数据通道数

parameter CODED_OUT_DW = 32 //编码后gt通道发送数据位宽

这些数据都可以根据实际情况再修改。

再根据上述数据,定义:

localparam FIFO_SEND_NUM = AD_IN_DW * AD_IN_CHANNEL / CODED_OUT_DW;

每次循环从fifo中读出FIFO_SEND_NUM个数据。

输入输出信号:

input rst_n , //复位信号

input clk_50M , //系统时钟50MHz

input ad_wr_clk , //fifo的写时钟

input coded_clk, //编码时钟,控制编码流程,并作为fifo的读时钟

input ad_en , //上升沿表明开始数据传输工作,下降沿表明结束数据传输工作

input wr_en , //写使能信号,高电平期间写入数据到fifo中

input [AD_IN_DW-1:0] ad_data , //写入的16位ad信号

output reg [CODED_OUT_DW-1:0] coded_data, //输出的编码信号

output reg [3:0] coded_ctr //输出的控制信号,用于控制数据对齐

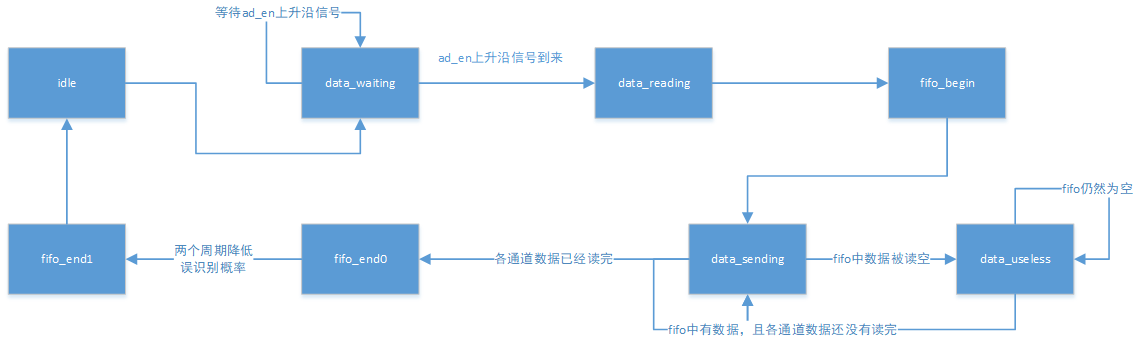

数据编码状态机:

整体流程如下:

- idle状态负责清空fifo,避免上次循环写进fifo中数据过多;

- data_waiting状态等待信号上升沿到来跳转到data_reading,并发送无效数据;

- data_reading状态在信号上升沿到来后,开始读取数据到fifo中;

- fifo_begin状态表明fifo即将传输数据,同时发送信号中会注释本次将要发送多少数据,一般就是FIFO_SEND_NUM个数据;

- data_sending状态将fifo中数据读出并通过gt通道发送过去;

- fifo_end0状态表明本次数据发送结束;

- fifo_end1状态与fifo_end0状态一起,通过两个特定信号,降低传输数据与标志信号重复的概率;

- 在data_sending状态中,如果出现提前将fifo中数据读空的情况,则跳转到data_useless状态,发送特定的无效数据,并等fifo中有数据填入后再跳回data_sending状态继续读出fifo发送数据。

解码模块设计

解码模块还需要根据修改后的编码模块,在原有代码基础上再进行一些对应的修改。暂时先依照编码流程,初步设计一个解码模块状态机,后面实际修改代码时,可能会有一些内容需要再修改。

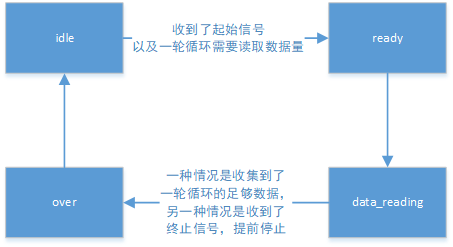

数据解码状态机:

整体流程如下:

- 没有收到数据起始信号时处于idle状态,等待数据到来,fifo写使能信号为低电平;

- 收到起始信号后,跳到ready状态,读取本轮需要读取的数据量,同时拉高fifo写使能信号,然后跳到data_reading状态;

- data_reading状态下,分析每次读取到的数据是否为有效数据;是,则写入到fifo中,同时计数器+1;否,则跳过该数据;

- 如果计数器达到了设定值,表明fifo收集到了足够的数据,则跳到over状态;如果提前收集到了终止信号,则同样跳到over状态;

- over状态下拉低fifo写使能信号,然后跳回到idle状态等待下一轮循环。

进展与后续计划

目前正在对编码模块进行对应修改,之后再将解码模块修改完善。学长给的模版中有个数据对齐模块,不太确定实际是否需要。调试好各个模块后再将各个模块拼接起来,上板子用信号发生器实际检测功能。

本文章使用limfx的vscode插件快速发布