通信协议设计

ad板卡采集数据通过SPI发送

这一部分将教程的代码进行了一些修改后封装为ip核,再整了个顶层代码后,上板子接上信号发生器测试了一下,可以正常显示出来信号发生器产生的波形。

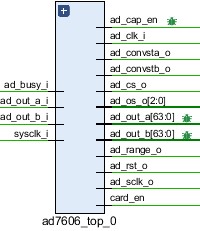

封装后的ip核如图。

其中,各个引脚功能:

-

输入引脚:

- ad_busy_i:ad7606忙标志位。

- ad_out_a_i:ad采集板卡采集模拟信号后转换的数字信号,其中a对应1~4路通道。

- ad_out_b_i:同上,其中b对应5~8路通道。

- sysclk_i:输入的系统时钟,代码里面调用clk_wiz_0模块通过系统时钟生成所需的其他时钟。

-

输出引脚:

- ad_cap_en:当该信号为高电平时,表明一次4路16位信号采集完成。

- ad_clk_i:将sysclk_i产生的100MHz时钟信号输出,用于为ila调试提供时钟信号。

- ad_convsta_o:convst从高到低后,AD转换开始,高电平期间将模拟数据转换为

- ad_convstb_o:同上。

- ad_cs_o:低电平期间,每个时钟ad_sclk_o进行数据的采样。

- ad_os_o[2:0]:ad7606 过采样倍率选择,本代码中设置为0,表明无过采样倍率。

- ad_out_a[63:0]:将接受的数字信号转换为64位信号输出,64位信号是由ad板卡上面1~4路16位信号通道组成的。

- ad_out_b[63:0]:同上,此处对应的是5~8路。

- ad_range_o:控制输入的模拟信号电平范围,当模拟信号真直流输入范围在±10V内时,输出高电平。

- ad_rst_o:输出ad板卡复位信号。

- ad_sclk_o:用于读取ad板卡数据,使用的是前面sysclk_i生成的15MHz时钟。

- card_en:表明ad板卡正常工作,常态高电平。

后面需要将采集到的数据通过gtp发送出去,因此重点需要理解数据采集后通过SPI传输的时钟时序与各个信号变化。

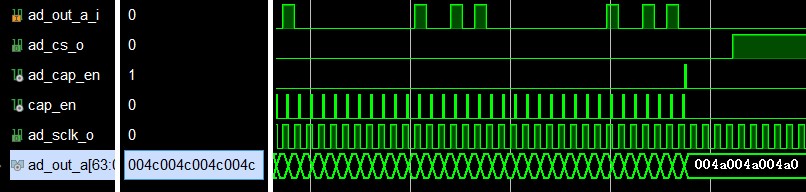

观察仿真信号波形:

以1~4路信号为例,标记为a。

可以看到,当CS信号为低电平时,每次sclk时钟周期会进行一次采集。每路信号为16位,16个时钟周期完成一路信号的采集。共4路信号,因此16*4=64个时钟周期后完成4路ADC采集。

在代码中,采样具体是通过移位操作完成的。每个时钟周期将ad_out_a_i的信号通过移位操作移入ad_out_a中,同时nbits进行一次计数。当nbits计数达到0'd64时,表明4*16位信号已经全部完成采集,ad_cap_en变为高电平。

在使用这个ip模块时,数据采集的方式可以理解成,每次ad_cap_en产生脉冲信号,ad板卡采样到的数据会完成更新。对于SPI发送过来的数据,可以借助于ad_cap_en信号,判断是否有新的数据发送过来。

需要注意,当CS信号变回低电平时,又会将新的数据移入ad_out_a中,因此只能在CS信号为高电平时读取ad_out_a。

5~8路信号同理。

后续工作

感觉需要像上面这样子,还需要把其他的各个数据传输的模块中,数据怎么传输出来、传输出来的数据怎么接收,都搞明白,理清楚其中关键信号的功能,再根据这些信号的规律设计数据传输协议,才容易补全模块代码。

本文章使用limfx的vscode插件快速发布