光模块官方教程代码调整

所使用IP模块配置步骤

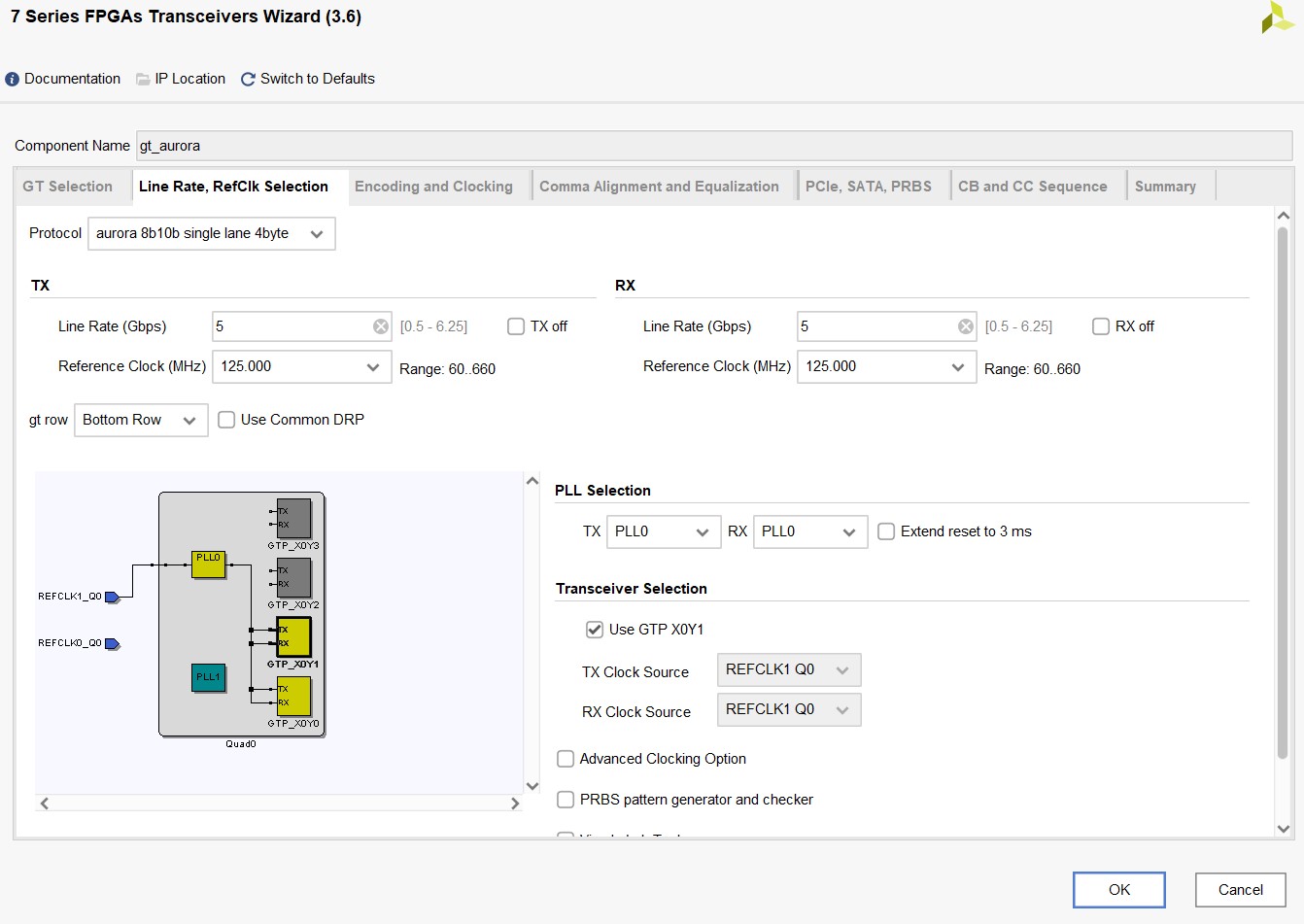

- 设置接口协议,根据板子差分晶振设置Line Rate与参考时钟;

- 设置速率与参考时钟,速率不能超过收发器最大速率,参考时钟需要与开发板上时钟一致;

本实验中使用的是双头光模块,设计就是把通道0的TX通过光模块短接到通道1的RX, 通道0的RX和通道1的TX没有使用到,需要选择GTP_X0Y0,GTP_X0Y1。

- 选择合适的用户时钟;

TXUSERCLK,和 RXUSERCLK时钟的选择概念必要重要,一般TXUSERCLK可以直接选择TXOUTCLK作为用户时钟,而RXUSERCLK,可以选择TXOUTCLK也可以选择RXUSERCLK,还可以选择RXPLLREFCLK作为用户时钟。这里就涉及到一个同步的概念,如果时钟不一致必须设置TX和RX的BUFFER,默认都是设置的。另外输入TX的发送时钟和RX的恢复时钟差异交大,可能会导致RX BUFFER的溢出或者读空,而导致数据出错。比较好的解决办法就是设置RXUSERCLK为RXOUTCLK,就是利用恢复时钟作为用户时钟,这样就很好的解决了同步的问题了。

- 不同的板子不同的环境,设置时钟校准,即每若干个字节发送一组CC Seq。

接收通道中同样有两个时钟域:从CDR恢复出的XCLK和接收通道工作时钟RXUSRCLK。RX通道使用RX Elastic Buffer 来桥接两时钟域,但由于两者细微的差异会使缓存变空或溢出。为此引入时钟矫正,在发送端周期性发送一些特殊字符,接收端在弹性缓存快满时删除这些字符,快空时复制这些字符从而保证缓存内数据维持动态平衡的状态。在前面设置TXUSERCLK和RXUSERCLK时同样也必须考虑这个问题。

工程文件结构

示例工程文件包含一个顶层exdes模块,由三部分组成,support是gtp收发模块,GEN是测试数据生成模块,CHECK是接收数据后的检查模块,查看接收是否正确。

原来文件中GEN模块里,数据读取后存储在rom寄存器里:

$readmemh("gt_rom_init_tx.dat",rom,0,511);

然后才将数据发送,与一直产生模拟数据并直接发送的要求不一致。

在后面工作中,GEN模块与CHECK模块需要被替换为自己的发送数据编码模块和接收数据编码模块。

gtp配置与修改

上周原计划内容:给的示例代码是使用单头光模块的,只使用 1 个通道进行环路测试,代码中只用了一个通道gt0(X0Y0)。而实验中使用的是双头光模块,因此会用到两个通道进行环路测试,需要增加进入新的通道gt1(X1Y1),将相关代码补充进去。

本周实际情况:

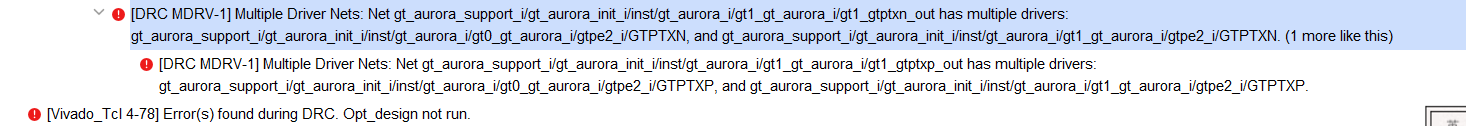

原先教程没有完全搞明白,里面有的步骤做错了,代码里就生成了一个通道gt0,以为通道gt1需要自己理解着把相关代码补进来,补充代码的事整了很久,而且到最后还是有问题解决不了,跑不起来代码。

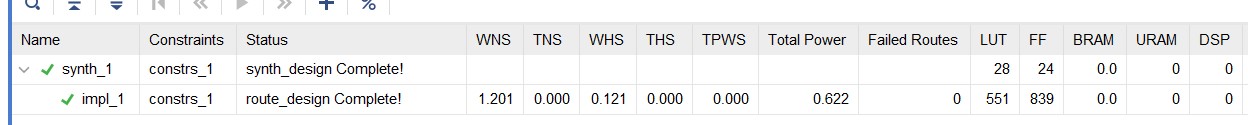

后来找学长问了教程看了代码,才发现自己一开始有的地方就做错了,gt1可以通过配置gt ip核自动生成相关代码,整个代码都可以自动生成出来,不需要自己手动补充通道gt1,只要按照教程内容修改里面少许的东西就可以符合要求。再重新按照教程步骤一步一步来,才把代码搞定。

本文章使用limfx的vscode插件快速发布