论文阅读_用于数字化传输到处理 FPGA 的高速数据链路优化

学习论文:用于数字化传输到处理 FPGA 的高速数据链路优化

( A High speed data link optimization for digitalized transfer to processing FPGA )

问题

ADC 板和运算 FPGA 之间的显著带宽不匹配,收发器数量有限,数据采集速率低于带宽,造成带宽浪费。

解决思路

通过时域多路复用,解决ADC 板和运算 FPGA 之间的显著带宽不匹配,从而允许使用低成本且收发器数量有限 FPGA。

效果示例:可以将多条线路从 1-5Gbps 组合到大约 5-20Gbps 的更高速度链路。

实现方式:

找到其他应用程序中使用的特定商业 ASIC (Application Specific Integrated Circuit,专用集成电路)来实现 TDM (例如,Texas 仪器的 TDM 系列可对 1-5 Gb 串行链路执行 2:1、4:1 或 8:1 多路复用)。

优点:直接降低了 FPGA 成本和设计,允许使用性能较低的 FPGA,并提供了使用 SOM(System on Module,嵌入式核心板)、COTS板的可能性。

SoM 是一个小型模块,它将 SoC 以及必要的存储器(如 RAM、闪存)、电源管理电路、时钟电路等集成在一个模块上,并提供标准化接口(如 GPIO、I2C、SPI、UART 等)供外部连接。SoM 通常直接焊接或插入到主板上使用。

COTS即Commercial Off-The-Shelf,翻译为“商用现成品或技术”或者“商用货架产品”,指可以采购到的具有开放式标准定义的接口的软件或硬件产品,可以节省成本和时间。

FMC(FPGA Mezzanine card,FPGA中间层板卡)

具有聚合概念的 IDM 中间层:

整个FMC模块由子板模块(或称中间层模块)、载卡两部分构成。

子板模块和载卡之间由连接器连接;子板模块上连接器使用公座(male),载卡上连接器使用母座(female)。

载卡连接器引脚与具有可配置IO资源的芯片(例如,FPGA)引脚通过PCB设计连接在一起;子板模块上连接器引脚与IO接口也是通过PCB设计连接起来。

子板PCB上可以设计不同的IO接口实现不同的功能,这样,同一个载卡可以通过子板的设计实现不同的扩展功能,使芯片的应用更加灵活。

按引脚数来分,有400引脚的FMC HPC(high pin connector)和160引脚的FMC LPC(low pin connector)。其排列方式为40行x10列,行由数字1-40排列,列由ABCDEFGHJK顺序表示,LPC相比于HPC行不变,列只有CDGH,且相应引脚定完全一致, 所以LPC和HPC在机械结构和电气特性上是可以互相兼容的。

FMC的引脚分为电源信号引脚、JTAG信号引脚、IIC信号引脚、地址设置引脚、相应的控制检测信号引脚、以及吉比特接口信号引脚(gigabit interface)和普通用户信号引脚(user defined pins)及其时钟信号引脚。其中的信号传输及其时钟信号引脚都是按照差分对标准来定义的。

吉比特接口信号(用DP表示,data pairs)引脚有20对,能够传输10组差分输入输出信号,其电平峰峰值不能超过1V,速度最大能够设计到10Gbit/s。

普通用户在使用时,FMC的部分引脚最好连接到同一个FPGA的Bank上面,保证其引脚电平相等。定义建议连到相同FPGA Bank的引脚分别称为bank A、bank B。对于低引脚数的FMC其bank A信号有34对,高引脚数的有58对,分别可以传输34对和58对差分信号;而bank B只在高引脚数FMC上有,信号对引脚有22对,可以传输22对差分信号。用户定义引脚信号电平采用LVDS和LVTTL信号标准,速度可以设计100Mbps到2Gbps。

Transceiver(高速收发器)

参考博客:xilinx的高速收发器构成原理和连接结构、Ultrascale/Ultrascale+ FPGA GTH IP及结构详解

应用场景:高速数据通信场景,如:千兆以太网、光纤通道、串行快速I/O接口等。

zynq UltraScale+ 的GTH最高线率约为13.1Gb/s。

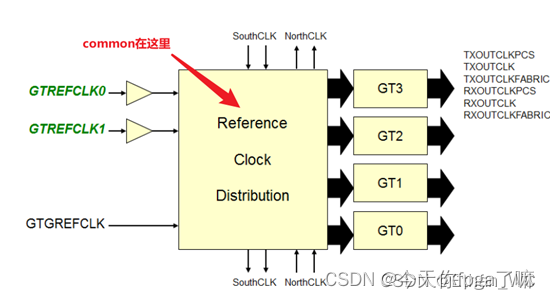

QUAD

高速接口是以 QUAD 为单位的, 4 对收发器(channel)组成一个 QUAD ,这是收发器的最小单元。

QUAD组成:

- 4个channel,每个channel包含一对收发器。

- 1个common(共享时钟资源),包含两个QPLL。

- 两个REFCLK(参考时钟)和专用的南/北时钟路径。

QUAD结构图:

注释:

- GTREFFCLK0/1 是参考时钟,是给高速接口内的 PLL 提供的参考时钟用于产生 PLL 输出时钟的。

- GTGREFCLK 是用于测试高速接口的测试时钟,一般用户不需使用,IBERT 这种测试软件可以使用。

- SouthCLK 是由相邻的上游 QUAD 提供的时钟,或者给相邻下游 QUAD 提供时钟,上图是一个独立的 QUAD。

- NorthCLK 是由下游的 QUAD 提供时钟,或者给相邻上游的 QUAD 提供时钟。

channel内部结构

一个channel包含一对tx和rx,每个链路有两个子层:PCS(物理编码子层)和 PMA(物理媒体连接子层)。

tx、rx分别代表发送数据线和接收数据线。

PCS 子层:包含 8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路; PMA 子层:主要进行串并、并串转换、预加重、去加重、串行数据的发送和数据时钟的提取。

tx链路数据处理过程:数据从FPGA逻辑层以并行形式输入,经过PCS层编码、插入控制字符和字对齐后,进入PMA层进行串行化、预加重处理,最终以差分信号的形式传输到物理介质。

详细内容:

- 数据从FPGA逻辑单元以宽度为8位、16位、32位甚至更宽的并行数据流的形式输入tx链路;

- 在PCS层(物理编码子层),输入的并行数据被编码成适合传输的格式,比如8b/10b编码,增加冗余位,以确保数据流中的直流平衡,并提供足够的信号转换来辅助时钟数据恢复(CDR);

根据协议的要求,在数据流中插入必要的控制字符(如帧开始SOF、帧结束EOF等),以帮助接收端识别数据帧的边界。

PCS层确保输入数据流中的字对齐,以保证在串行化过程中不会出现位错乱。 - 编码后的并行数据在PMA层(物理介质连接子层)被转换为高速串行数据流;

可能会通过增强信号的高频成分来提高信号完整性,对串行信号进行预加重,以补偿信号在长距离传输中的高频衰减;

通过差分对(例如CML或LVDS)发送到物理传输媒体(如铜线、电缆、光纤等)。

数据的直流平衡(DCBalance):在传输数据时,信号的高低电平出现的频率大致相等,从而使得信号的平均电压接近零或一个恒定值。

作用:简化时钟数据恢复(CDR)、减少直流偏移、改善传输距离和质量.

rx链路数据处理过程:数据以差分串行信号从物理介质输入,经过PMA层的CDR、均衡、串行到并行转换,进入PCS层进行解码、字对齐和控制字符处理,最终以并行形式输出到FPGA逻辑层。

详细内容:

- 从物理传输媒体接收的差分串行数据首先进入PMA层。

- PMA层对接收到的信号进行均衡,以补偿传输过程中高频损失和其他信号失真,改善信号完整性、降低误码率;

通过时钟数据恢复模块从接收的串行数据流中提取嵌入的时钟信号,并使用该时钟对数据进行采样;

经过均衡和采样的串行数据在PMA层被转换回并行格式。 - 在PCS层,接收到的并行数据被解码回原始格式(例如从10位解码为8位);

对数据流进行字对齐;

识别并处理从发送端传输过来的控制字符(如SOF、EOF等),用于确定数据帧的边界和其他协议信息。

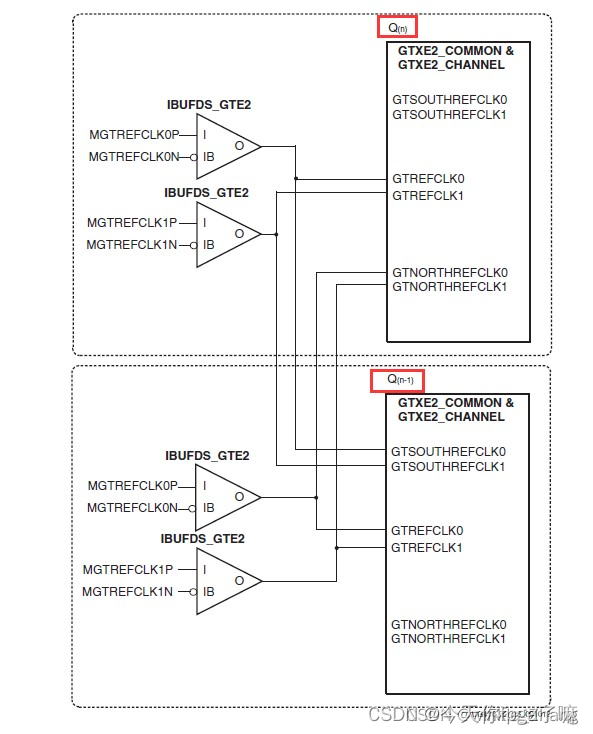

时钟

因为每一个QUAD有两个外部参考时钟,因此对于每一个QUAD来说,可以选择两个不同的参考时钟,每一个CHANNEL的接收端和发送端都可以独立选择参考时钟,可以选择GTREFFCLK0或GTREFFCLK1。

此外,还可以使用其他Quad的参考时钟(south clk 或 north clk)。

在图中可以看到,REFCLK进来必须要经过一个IBUFDS_GTE,完成差分转单端。

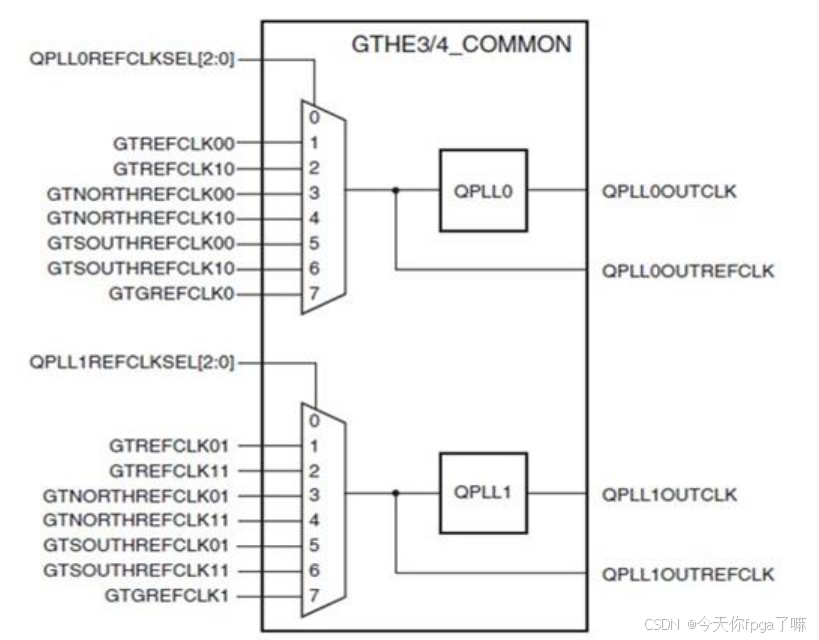

mux可以根据QPLL0REFCLKSEL和 QPLL1REFCLKSEL 选择不同时钟输入端。如下图:

QPLL,其中的Q含义就是QUAD,即一个GTX QUAD公用的PLL。

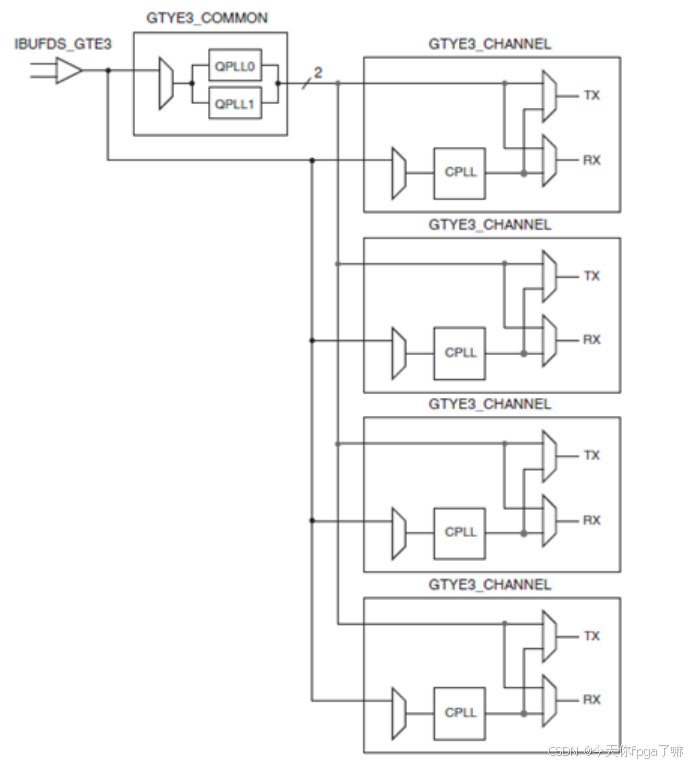

高速接口时钟连接网络结构:

时钟资源可以布线到任意一个 common 和 channel。每个 QUAD 有一个COMMON 和四个 CHANNEL。高端的高速接口 CHANNEL 中有 CPLL,低端的 GTP 没有 CPLL。

CPLL,即Channel PLL,含义是每一个Channel单独拥有的PLL。

本文章使用limfx的vscode插件快速发布