FPGA学习_ADC

编写测试文件过程:

- 产生模拟激励(波形);

- 将产生的激励加入到被测试模块中并观察其响应;

- 将输出响应与期望值相比较。

时钟激励设计

使用forever:

parameter ClockPeriod=10; //周期为10ns

initial

begin

clk_i=0;

forever

#(ClockPeriod/2) clk_i=~clk_i; //50%占空比时钟

end

使用always:

parameter ClockPeriod=10;

initial

begin

clk_i=0;

end

always #(ClockPeriod/2) clk_i=~clk_i; //50%占空比时钟

产生固定数量时钟脉冲:

parameter ClockPeriod=10;

initial

begin

clk_i=0;

repeat(6) //循环六次

#(ClockPeriod/2) clk_i=~clk_i;

end

高低电平时间不均等,占空比不为50%的时钟:

initial

begin

clk_i=0;

forever

begin

#((ClockPeriod/2)-2) clk_i=0; //低电平为3ns

#((ClockPeriod/2)+2) clk_i=1; //高电平为7ns

end

end

SPI(Serial Peripheral interface,串行外围设备接口)

讲解链接:SPI原理超详细讲解---值得一看 特点:高速,全双工,同步

主从模式

SPI系统包括主设备与从设备。

主设备:有且仅有一个,提供时钟,读写信号由主设备发起。

从设备:一至多个,接收时钟,存在多个从设备时,通过各自的片选信号进行管理。

SPI四条信号线

- MISO: 主设备输入/从设备输出引脚。该引脚在从模式下发送数据,在主模式下接收数据。

- MOSI: 主设备输出/从设备输入引脚。该引脚在主模式下发送数据,在从模式下接收数据。

- SCLK:串行时钟信号,由主设备产生。

- CS/SS:从设备片选信号,由主设备控制。它的功能是用来作为“片选引脚”,也就是选择指定的从设备,让主设备可以单独地与特定从设备通讯,避免数据线上的冲突。

在硬件上表现为,MISO、MOSI、SCLK为一条线,而SS信号线则与从设备数量有关。

SPI数据交换

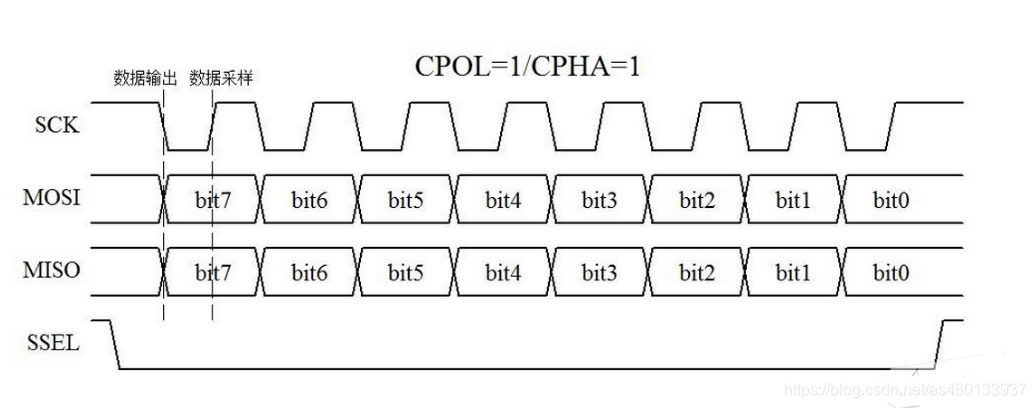

信号变化过程如上图。

SPI数据发送过程:

信号变化过程如上图。

SPI数据发送过程:

- 首先拉低对应SS信号线,表示与该设备进行通信。

- 主机通过发送SCLK时钟信号,来告诉从机写数据或者读数据。

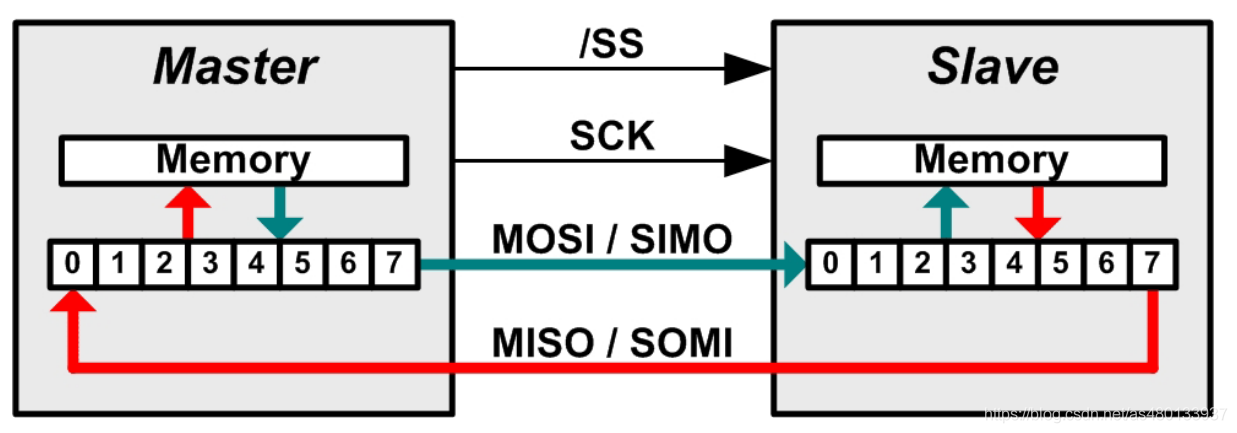

这里要注意,SCLK时钟信号可能是低电平有效,也可能是高电平有效,因为SPI有四种模式,这个我们在下面会介绍。图中的下降沿提示数据输出,上升沿进行数据采样。 - 主机(Master)将要发送的数据写到发送数据缓存区(Menory),缓存区经过移位寄存器(0~7),串行移位寄存器通过MOSI信号线将字节一位一位的移出去传送给从机,同时MISO接口接收到的数据经过移位寄存器一位一位的移到接收缓存区。

- 从机(Slave)也将自己的串行移位寄存器(0~7)中的内容通过MISO信号线返回给主机。同时通过MOSI信号线接收主机发送的数据,这样,两个移位寄存器中的内容就被交换。

具体交换过程如图所示:

SPI外设的读写操作是同步进行的。如果只想进行写操作,则每次从设备都需要发送一次空字节;如果想进行读操作,则每次都需要主设备向从设备发送一个字节。简而言之,你发一个数据必然会收到一个数据;你要收一个数据必须也要先发一个数据。

SPI外设的读写操作是同步进行的。如果只想进行写操作,则每次从设备都需要发送一次空字节;如果想进行读操作,则每次都需要主设备向从设备发送一个字节。简而言之,你发一个数据必然会收到一个数据;你要收一个数据必须也要先发一个数据。

主机与从机均有移位寄存器,且二者相连成环,当寄存器中的内容全部移出时,相当于完成了两个寄存器内容的交换。

SPI通信模式

时钟极性(CPOL)定义了时钟空闲状态电平:

- CPOL=0,表示当SCLK=0时处于空闲态,所以有效状态就是SCLK处于高电平时

- CPOL=1,表示当SCLK=1时处于空闲态,所以有效状态就是SCLK处于低电平时

时钟相位(CPHA)定义数据的采集时间。

- CPHA=0,在时钟的第一个跳变沿(上升沿或下降沿)进行数据采样。在第2个边沿发送数据

- CPHA=1,在时钟的第二个跳变沿(上升沿或下降沿)进行数据采样。在第1个边沿发送数据

总共四种状态,区别是定义了在时钟脉冲的哪条边沿转换(toggles)输出信号,哪条边沿采样输入信号,还有时钟脉冲的稳定电平值(就是时钟信号无效时是高还是低)。

所需关注时序要求

- 接口器件需要注意最高接口速度。如已知fmax=10MHz,则设计SPI接口时钟可以使用100KHz的频率。

- 建立时间和保存时间。数据为了可以正确打入D触发器需要有足够的建立时间有保存时间,因此需要注意器件tsu(minimum setup time)与th(minimum hold time)。

- LATCH CLOCK和SHIFT CLOCK。该数据需要满足建立时间和保持时间要求。

ADC7606

芯片功能概述

需要理解其中各类数据的意义。

文档复制内容:

DAQ7606 数据采集卡,AD 转换芯片为AD7606-8,AD760-8 是16 位8 通道同步采样模数数据采集系统(DAS)。AD7606 内置模拟输入箝位保护、二阶抗混叠滤波器、跟踪保持放大器、16 位电荷再分配逐次逼近型ADC、灵活的数字滤波器、2.5V 基准电压源、基准电压缓冲以及高速串行和并行接口。AD7606 采用5V单电源供电,可以处理±10V 和±5V 真双极性输入信号,同时所有通道均能以高达200 kSPS 的吞吐速率采样。输入箝位保护电路可以耐受最高达±16.5V 的电压。无论以何种采样频率工作,AD7606 的模拟输入阻抗均为1 MΩ。它采用单电源工作方式,具有片内滤波和高输入阻抗,因此无需驱动运算放大器和外部双极性电源。AD7606 抗混叠滤波器的3 dB 截止频率为22 kHz;当采样速率为200 ksps 时,它具有40 dB 抗混叠抑制特性。灵活的数字滤波器采用引脚驱动,可以改善信噪比(SNR),并降低3 dB 带宽。

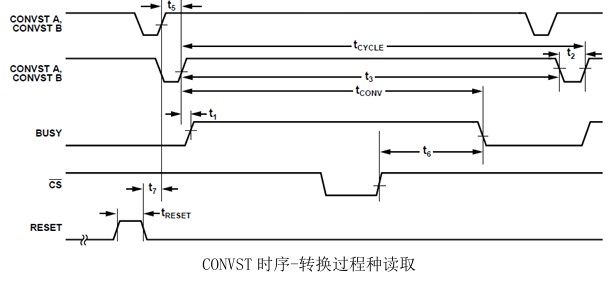

ADC转换控制时序

工作时序分为两种:CONVST 时序-转换之后读取、CONVST 时序-转换过程种读取。其中,必须采用第二种工作时序,才能确保200Kbps的采样率。

图中信号功能:

- RESET 信号用于对 AD7606 芯片的复位,复位的高电平时间参数。tRESET=50ns,复位和转换信号CONVSTA/ONVSTB的上升沿时间参数t7=25ns

- CONVSTA/ CONVSTB的低电平时间参数t2=40ns。

- CONVSTA/ CONVSTB如果不是同步,那么他们之间的时间差不能超过t5=0.5ms,我们这里是同时的。

- 转换周期tCYCLE=5us。

- BUSY信号为高电平代表数据正在转换,转换时间参数tCONV为最大4.15us。

- CS信号和BUSY信号有一个时间参数t6不能大于25ns。

本周工作内容

- 阅读教程与网上资料,学习SPI通信相关内容

- 使用Vivado进行基本实践,思考巩固SPI通信中相关知识,并通过SPI驱动HC595点亮数码管实验思考SPI相关程序设计的要点

- 开始阅读AD转换芯片相关知识内容

当前疑惑与后续规划

- 存在较多相关数据,还不能理解其中含义与意义,需要更多理解

- 相关代码继续理解并实践

本文章使用limfx的vscode插件快速发布