龙哥程序修改

程序验证,问题及解决

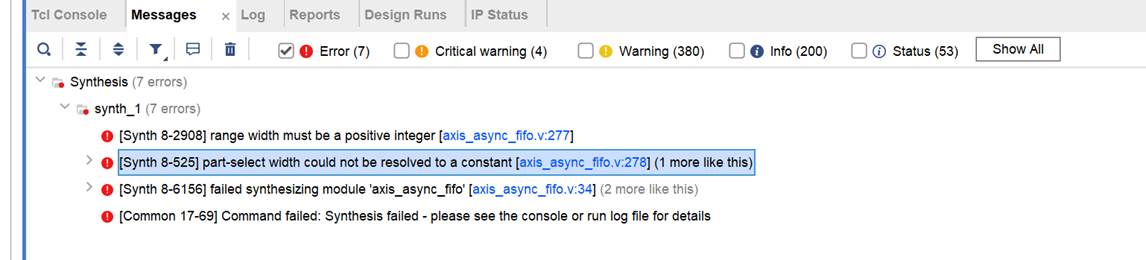

拿到龙哥的10G_UDP Vivado工程项目,打开,综合,报错,报错信息如下:

然后点进去axis_async_fifo.v这个文件看,看了半天觉得不是这个文件的问题,然后看调用这个模块的文件,一开始找到UDP模块用了这个fifo,以为是UDP模块里可能有问题,然后研究了半天又没发现问题,走不通了没事干,就看看别的文件,然后发现另一个文件blob_fifo_udp_transmit.v也调用了axis_asynv_fifo,然后研究了下这个文件,发现导致问题的原因了:

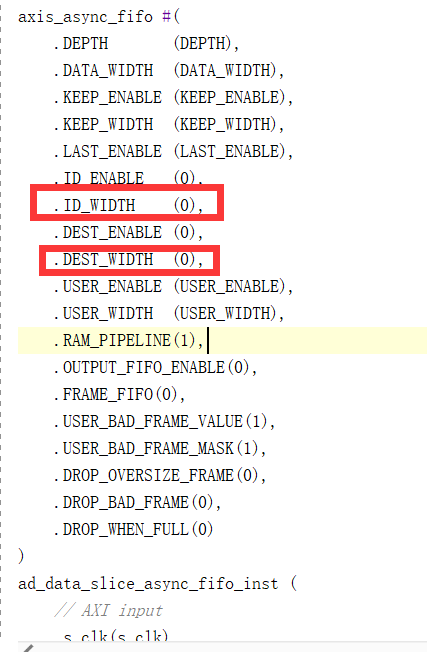

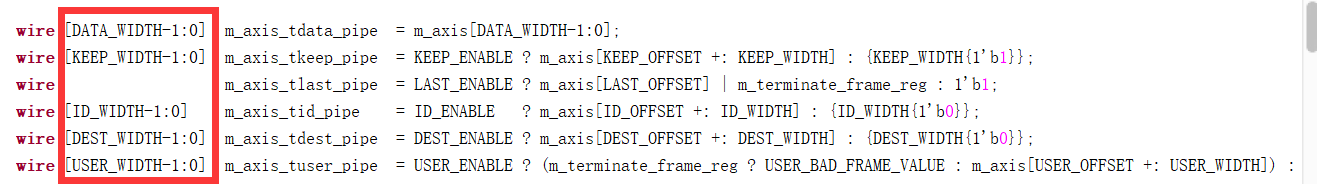

如图所示,红框处代码有两个参数WIDTH都是0,而在axis_async_fifo中都用到了这两个参数

红框处可以看到,有很多处数据的位宽是ID_WIDTH-1如果ID_WIDTH为0,那0-1=-1,位宽为负数那肯定报错,所以把这两个为0的WIDTH注释掉(相当于使用默认参数WIDTH=8)就好了,问题得到解决

无法将top文件添加到BD中

要融合我的工程和龙哥的工程,需要将龙哥工程的顶层文件ad_blob_udp_top添加到Block Design中,但很遗憾无法添加,于是我查找原因:

根据Vivado 官方文档(UG994),下面三种类型的文件无法添加到Block Design中:

有语法错误 的模块

缺少源文件 的模块

包含或引用EDIF网表、DCP文件、另一个Block Design或不支持的IP核 的模块

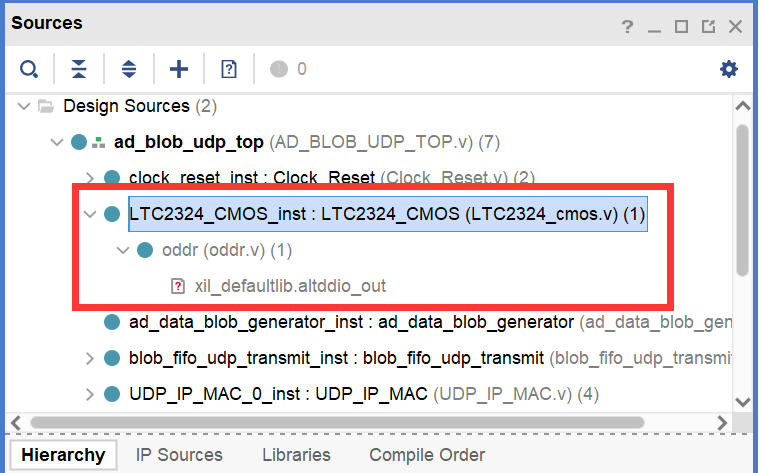

然后如果一个文件(模块)下用到的文件有刚才那三个问题,也会导致顶层文件无法被添加到Blocl Design中

逐个文件尝试后,发现问题在这个ODDR.v文件上,理论上这个文件是存在的,综合的时候Vivado能找到这个文件,不报错,但要添加进Block Design时Vivado就找不到这个文件了

解决方法是再创建一个oddr文件,内容与原来的相同,但Vivado就能发现这个文件了

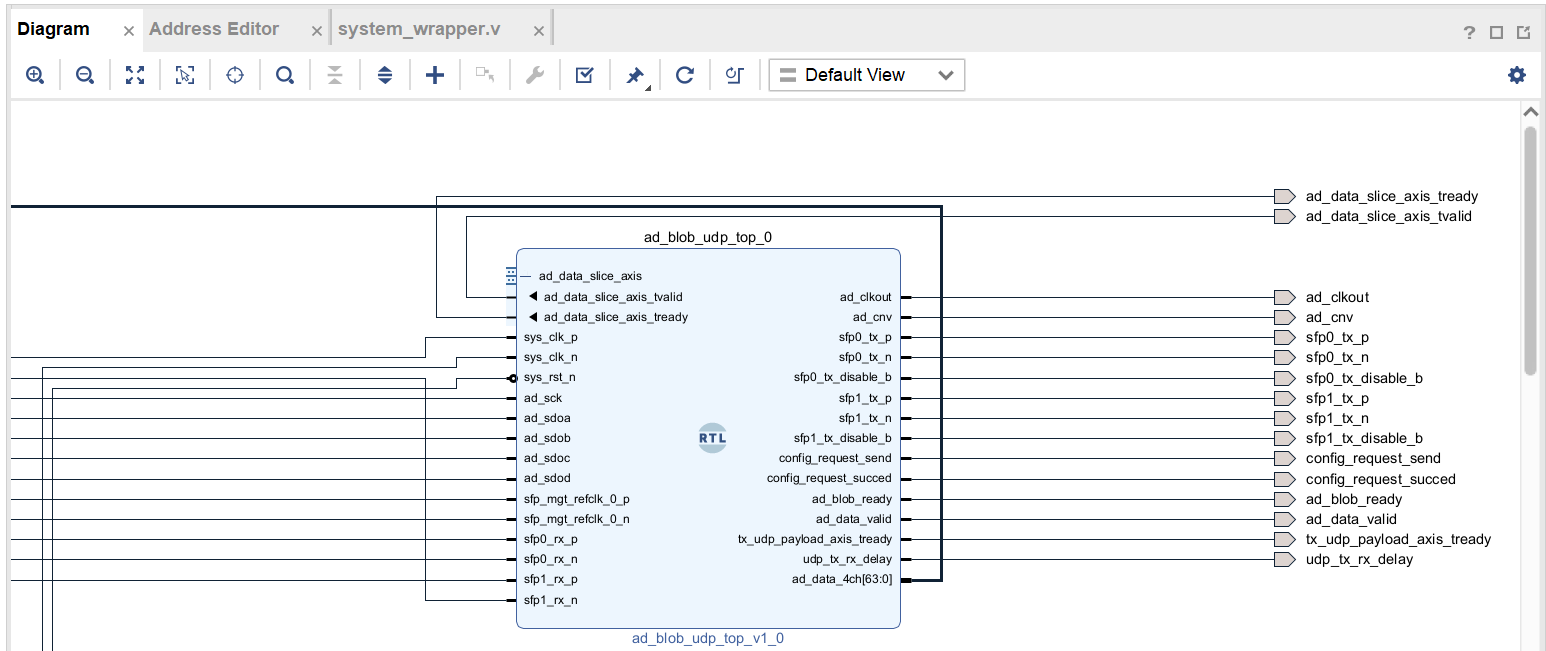

然后成功将ad_blob_udp_top添加进Block Design中

融合两个工程

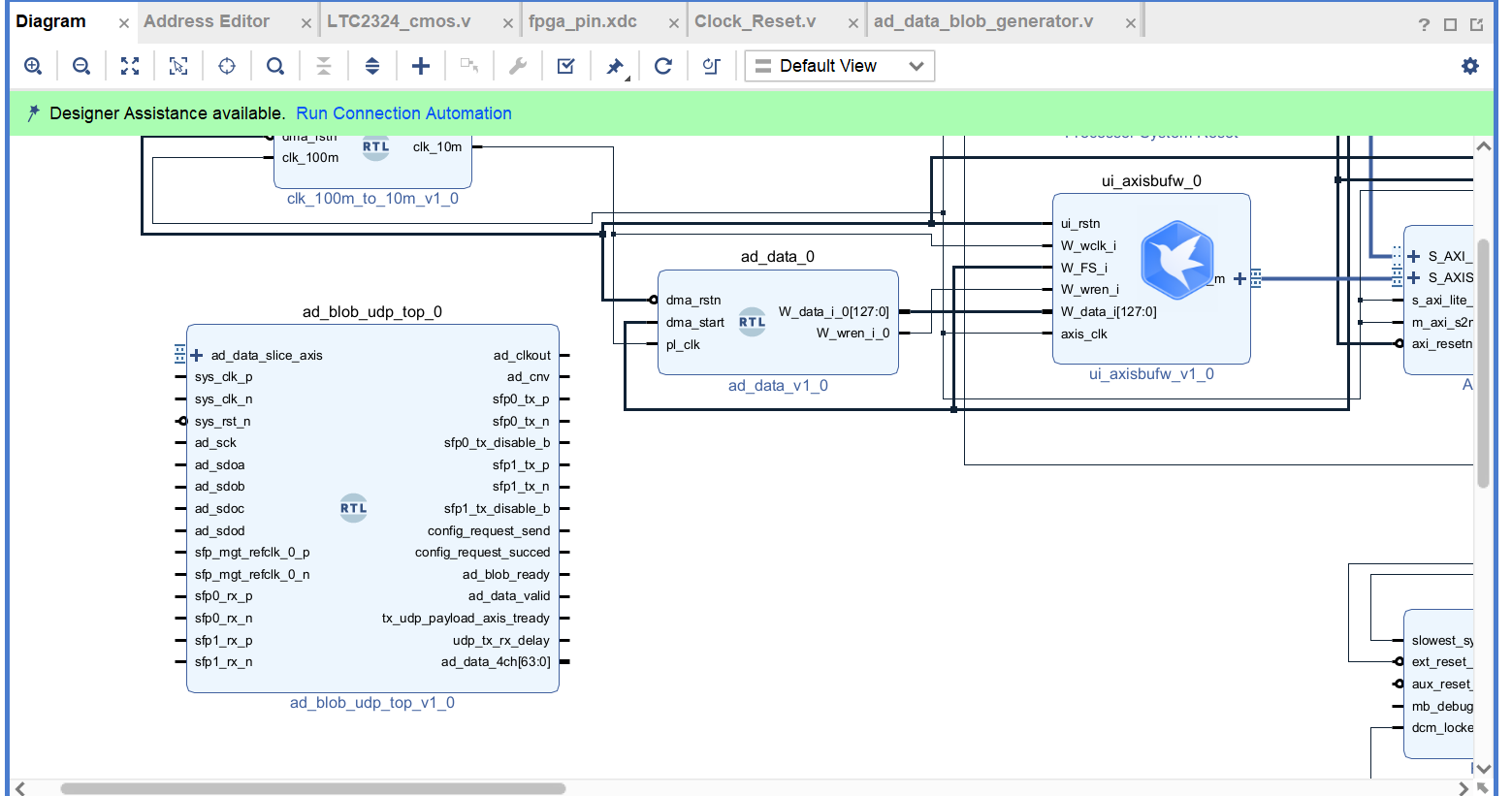

主要工作是给这个模块连线,引出ad信号到dma前的模块

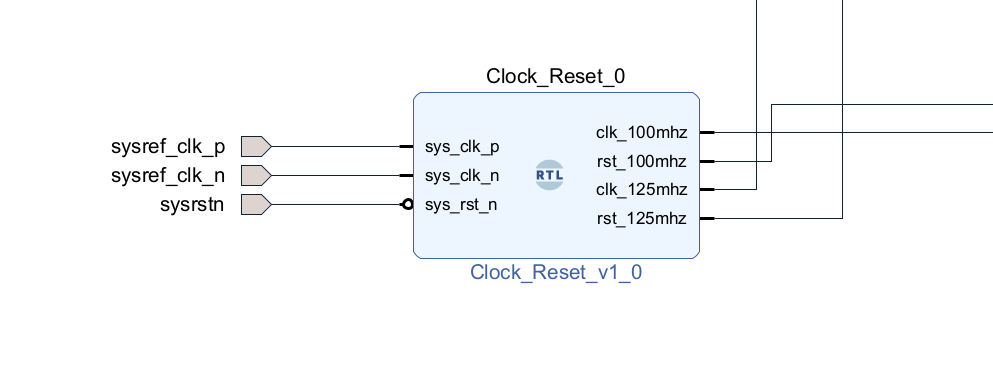

然后时钟方面两个工程有两个时钟,可以合成一个模块共用

然后验证一下Block Design没有问题,就可以Generate Output Product,Create HDL Wrapper

将龙哥的约束文件fpga_pin.xdc和我的合并,有些重合的引脚可以去掉

然后综合,生成比特流

使用Vitis生成必要文件

虚拟机生成BOOT文件,放置sd卡

待测试,待续未完

本文章使用limfx的vscode插件快速发布