10G UDP测试与AD板卡设计

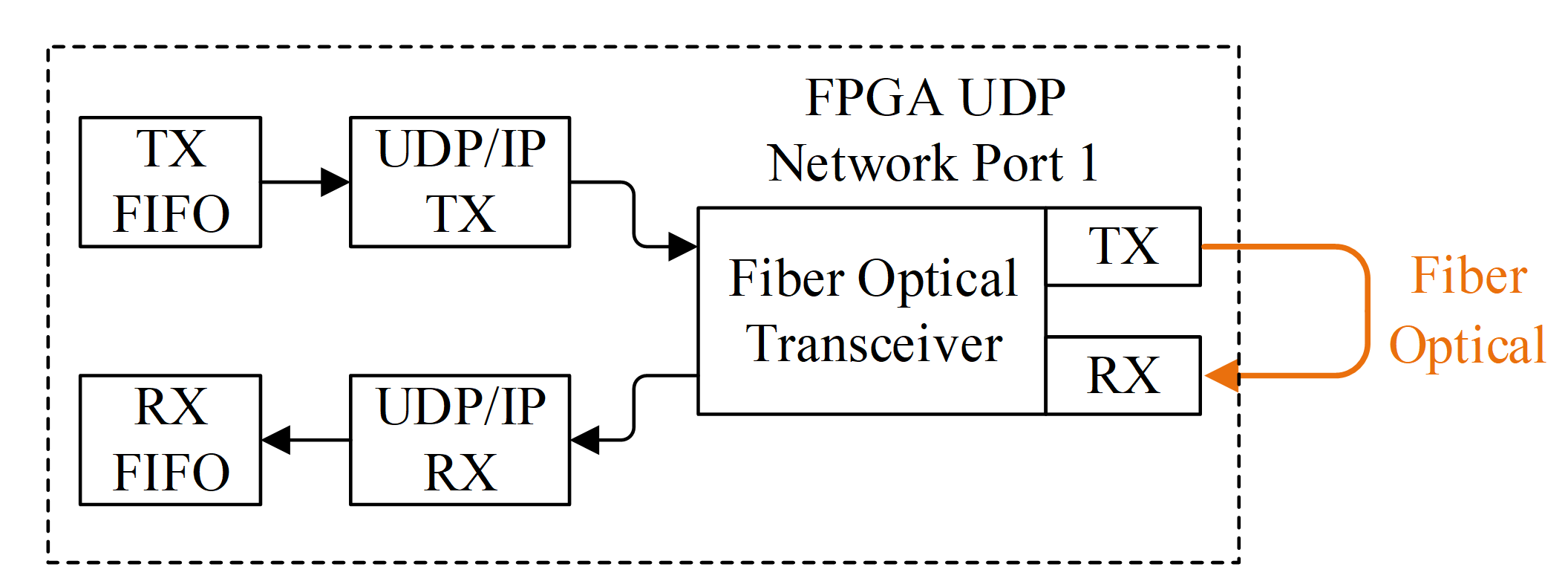

10G UDP Echo 测试

-

测试接线采用

SFP+光收发器,具备TX与RX两个数据端口。测试时将 TX 与 RX 直接短接,形成自回环。

-

数据包:1448个字节。10G UDP网络协议栈采用

64bits数据宽度,数据包长度需要是8的整数倍。注意,由于整个协议栈不支持MTU,因此当 UDP 数据包长度大于 1472 字节时网络协议栈将会抛弃该包。 -

数据发送方式:轮询,即循环发送。

-

数据协议栈驱动时钟:156.24MHz。

-

数据收发观测:采用IO电平观测,正在接收或发送为高电平,其余状态为低电平。

-

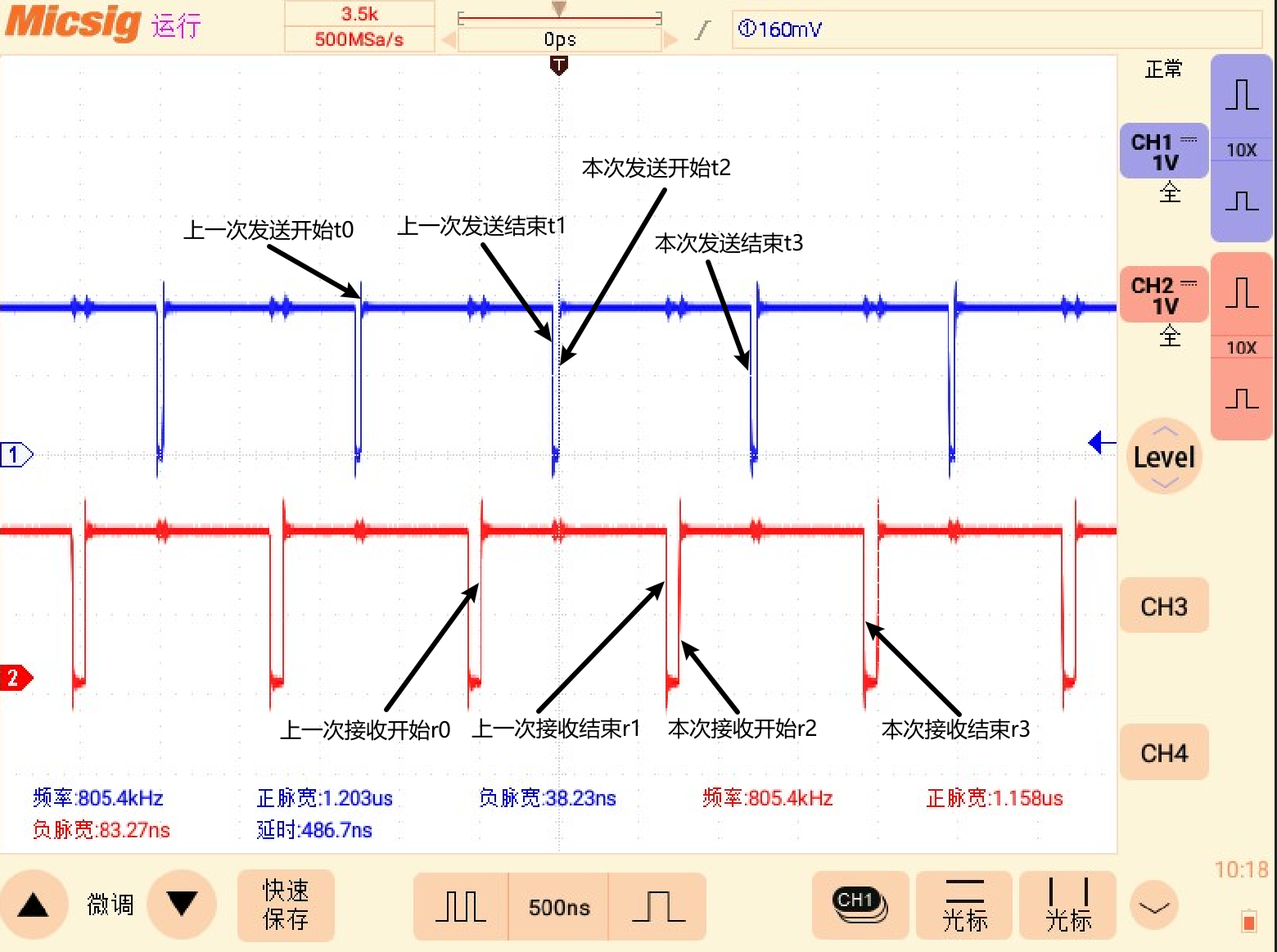

测试结果如下。具体参考文档11

-

接收周期等于发送周期,说明接收无丢包。

-

理论数据带宽:14488805.4k = 9.33Gbps。当采用1472字节的数据包时,收发周期时801.3kHz,数据带宽为9.44Gbps,基本占据所有数据带宽。

-

数据链路编码与传输阶段时延:t0-r0时延或t2-r2时延。基本可以认为是数据链路编码时延,为754.3ns。

-

RTT:t0-r1或t2-r3,为1.912us。对于双端口UDP Echo,预估为5-6us。

-

AD Board设计

-

主要构成:模拟接口,前端,ADC,数据接口。

-

模拟接口:

VHDCI 68接口。

-

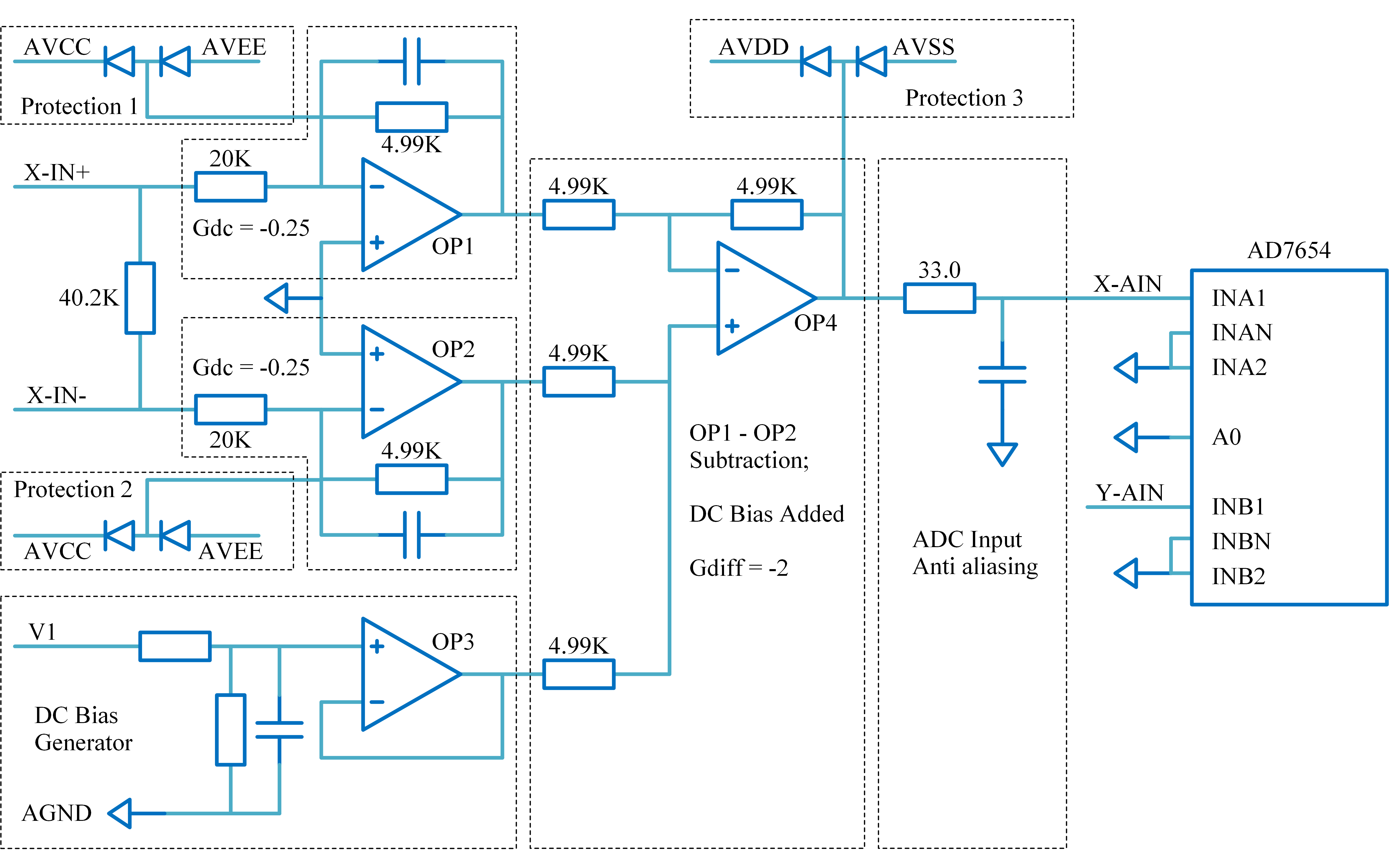

前端电路:典型前端为ADQ196CPCI。包括一下几个部分:

-

输入预衰减,针对输入电压较高或者有很高共模电压的信号。

-

输入保护:限制输入到运放的引脚电压不超过运放供电电压。

-

运放电路:提供增益调节和差分转单端操作。增益部分可以加入电容提供-20dB的衰减项。

-

抗混叠:运放电路输出到ADC输入端,将带宽外的信号进行衰减。

-

-

ADC:AD7616,LTC2325。目前采用AD7616,设定位

硬件工作模式,由FPGA进行时序控制。AD7616还有软件模式,需要读写寄存器。数据采用16位并口输出。 -

数据接口:B2B端子。

Reference

本文章使用limfx的vscode插件快速发布